Ein umfassender Leitfaden zu unserem PCB-Herstellungsprozess

ENTWURFSPRÜFUNG UND VORBEREITUNG DER PRODUKTIONSWERKZEUGE.

Die erste Phase des PCB-Herstellungsprozesses umfasst eine Überprüfung des vom Designer bereitgestellten Fertigungsdatenpakets und die Vorbereitung der Fertigungswerkzeuge und CAM-Daten.

Produktionsdatenpaket

Das Ergebnis des PCB-Herstellungsprozesses ist ein Datenpaket, das dem Hersteller in einem Industriestandardformat - Extended Gerber oder ODB++ - zur Verfügung gestellt wird. Die Gerber-Dateien definieren die Kupferlagen, Lötmaskenlagen und Bauteilbezeichnungen. Darüber hinaus enthält das Fertigungsdatenpaket eine Bohrdatei, eine Netzliste und allgemeine Spezifikationen.

Design für die Fertigung

Die Ingenieure prüfen das Datenpaket und stellen sicher, dass alle für die Fertigung erforderlichen Informationen klar und vollständig sind. Wir prüfen auch, ob das Design und die Spezifikationen mit den Fertigungsmöglichkeiten übereinstimmen.

Sobald alle technischen Fragen geklärt sind, werden die notwendigen Werkzeuge für die Produktion vorbereitet.

Vorbereitung der Produktionsplatten.

Die Hersteller verwenden Standard-Fertigungspaneele. Das Fertigungspanel muss unter Berücksichtigung der Leiterplattenabmessungen und entsprechenden Fertigungsanforderungen wie z.B. Prozesskontrollcoupons, Werkzeuglöcher und Handhabung designed werden

Arbeitsfilm (Fotowerkzeuge) Vorbereitung.

Mit Hilfe eines Laserplotters wird für jede Leiterplattenbestückung ein Film erstellt. Der Laserplotter befindet sich in einer Dunkelkammer mit kontrollierter Temperatur und Feuchtigkeit. Die Filme werden aufeinander abgestimmt, um eine perfekte Ausrichtung zwischen den Schichten zu gewährleisten.

Die gestanzten Registrierlöcher werden später zur Ausrichtung der Filme im UV-Belichtungsprozess verwendet. Eine andere Methode ist die Laserdirektbelichtung (LDI), bei der eine CCD-Kamera in der Belichtungsmaschine verwendet wird, um das Fototool zu registrieren.

Innere Lagen

Zur Vorbereitung der inneren Schichten nehmen wir ein Basismaterial aus Epoxidharz und Glasgewebe, das beidseitig mit Kupferfolie beschichtet ist, und entfernen das überschüssige Kupfer, damit nur dort Kupferspuren verbleiben, wo wir sie für die Realisierung der elektrischen Schaltung benötigen.

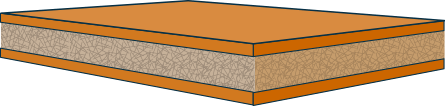

Grundmaterial

Der Kern der inneren Schicht besteht aus Epoxidharz und einem Glasfasergewebe, das beidseitig mit einer dünnen Schicht Kupferfolie beschichtet ist. In den meisten Fällen wird FR4-Material verwendet.

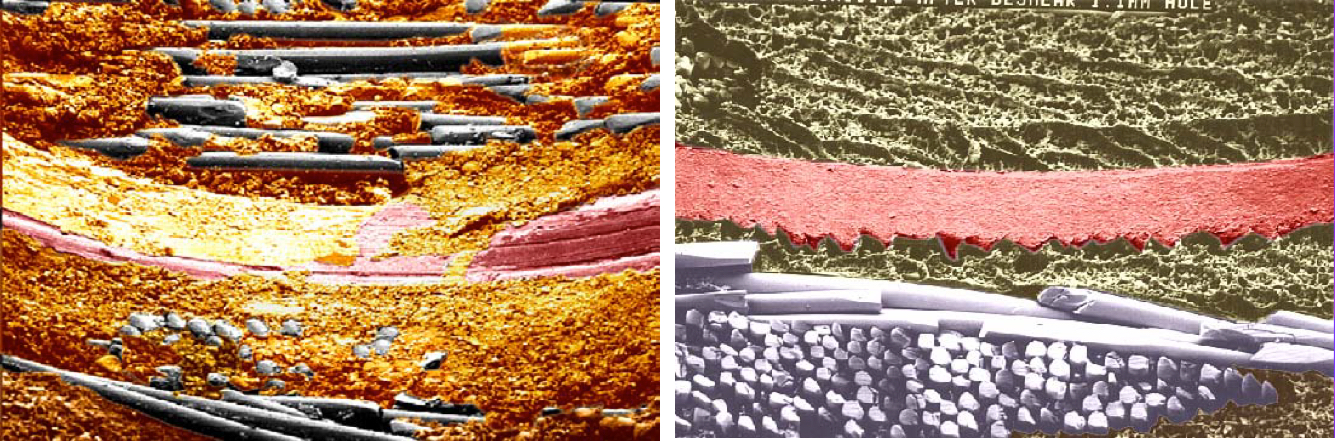

Das beidseitig plattierte Kupfer wird durch ein chemisches Reinigungsverfahren für Innenschichten von Oxiden und möglichen Verunreinigungen befreit. Gleichzeitig rauen die rotierenden Bürstenwalzen die Kupferoberfläche auf, um eine ausreichende mechanische Haftung zu gewährleisten.

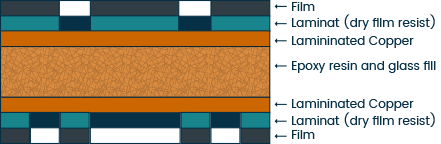

Trockenfilm-Laminierung

Das Kernmaterial wird durch ein beheiztes Walzenpaar geführt (Temperatur: ca. 110º C Druck: 3-5 BAR). Die Cu-Oberfläche wird empfindlich für UV-Licht, daher erfolgt die weitere Verarbeitung nur im Gelblichtbereich.

Exposition auf inneren Schichten

Die Folie für die Schicht wird auf das laminierte Material gelegt und die Laminatschicht wird einer energiereichen UV-Lampe ausgesetzt. Die Leiterbahnen der Leiterplatte sind in der Folie transparent und das darunter liegende Laminat wird mit UV-Licht bestrahlt. Der belichtete Bereich wird chemisch polymerisiert und die Leiterbahnen härten aus.

Der Bereich, der vom schwarzen Teil des Films bedeckt ist, polymerisiert nicht und kann im Entwicklungsprozess weggewaschen werden.

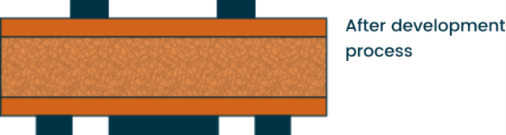

Entwicklungsprozess

Die Entwicklung erfolgt durch horizontales Besprühen der inneren Schichten mit einer Natriumkarbonatlösung und anschließendes Abspülen mit Süßwasser und Trocknen. Die nicht belichteten Bereiche werden nun entfernt.

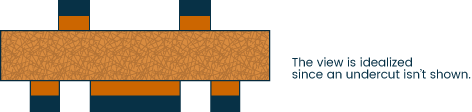

Ätzen des inneren Schichtkerns

Die Innenseite wird ein weiteres Mal besprüht, abgespült und getrocknet. Diesmal mit einer sauren Lösung. Durch diesen Prozess wird das Kupfer aus dem freiliegenden Bereich entfernt, so dass nur noch Kupfer in den Spuren und Pads übrig bleibt.

Die Kupferdicke der Schichten bestimmt die Geschwindigkeit des Prozesses. Dickere Kupferschichten begrenzen die Feinheit des leitfähigen Musters.

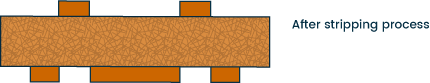

Strippen

Die Lackschicht wird entfernt, indem das Material durch eine Ätznatronlösung geleitet wird.

Automatische optische Inspektion (AOI)

Die Innenlagen werden einer automatischen optischen Prüfung unterzogen, um Unterbrechungen und Kurzschlüsse sowie korrekte Schaltkreisgeometrien im Vergleich zu den ursprünglichen Entwurfsdaten zu erkennen.

Braun-Oxid-Zubereitung

Die inneren Schichten werden einer chemischen Oberflächenvorbereitung unterzogen, um die Oberfläche aufzurauen und die Haftung zwischen dem PREPREG-Harz und der Kupferoberfläche im Laminierungsprozess zu verbessern.

LAMINATION

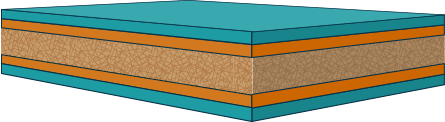

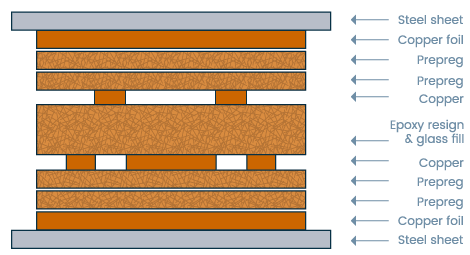

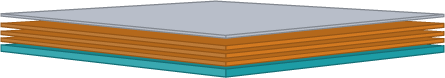

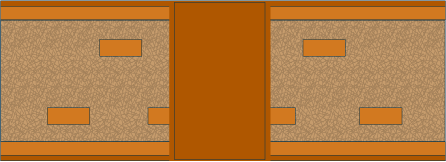

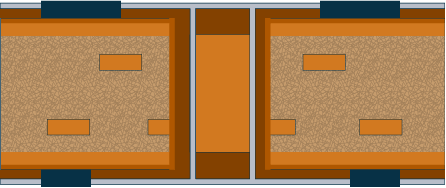

Material-Aufbau

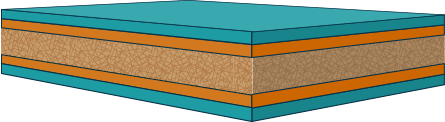

Die Schichten werden vor dem Laminieren übereinander gestapelt. Beginnend mit einer Kupferfolie am unteren Ende (die für den Aufbau der unteren Außenschicht verwendet wird). Auf die Kupferschicht werden PREPREG-Schichten gelegt, auf das PREPREG die Innenschichten, getrennt durch PREPREG-Schichten, und auf die Innenschichten PREPREG-Schichten und eine zweite Kupferfolie (die zum Aufbau der oberen Außenschicht verwendet wird).

PREPREG ist ein teilweise ausgehärtetes Epoxidharz mit Glasfasern, das vom PREGREG-Hersteller polymerisiert wird. Es wird als Isoliermaterial und Klebstoff zwischen den Schichten der Leiterplattenkomponenten verwendet.

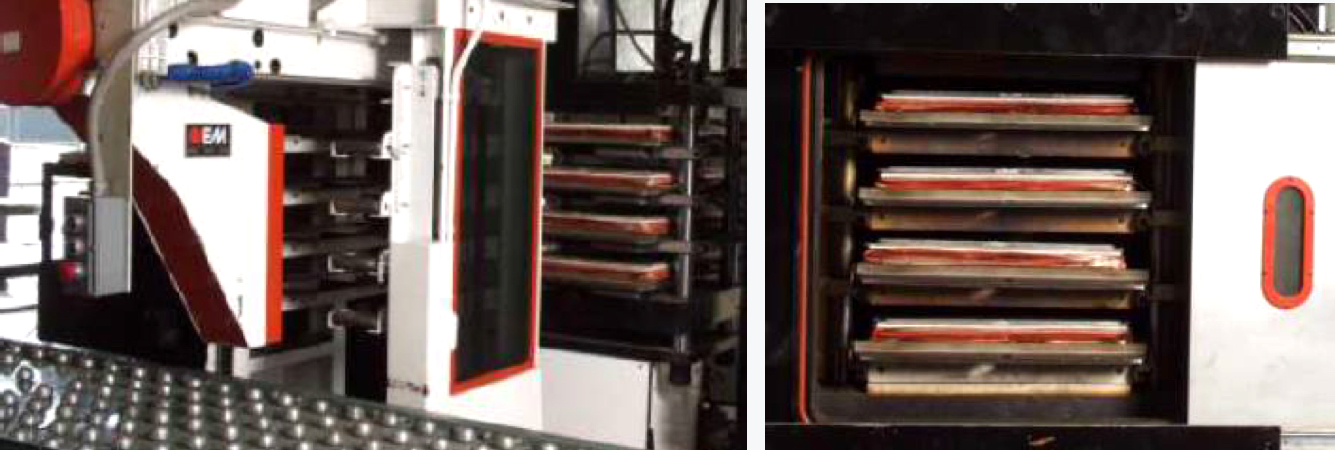

Hochdruck-Laminierung

Die übereinander gestapelten Lagen werden unter Vakuum, hoher Temperatur und hohem Druck laminiert. Mehrere Leiterplatten, die durch Trennwände getrennt sind, werden gleichzeitig gepresst. Durch die Hitze und den Druck schmilzt und härtet das Epoxidharz im PREPREG, während der Druck die Leiterplatte verschmilzt.

Beschneiden

Der Flash (Material, das aus der laminierten Platte herausragt) wird abgefräst, so dass eine saubere Platte übrig bleibt, die wie ein Stück Laminat aussieht.

BOHRUNGEN

X-RAY-Analyse

In einer vorbereitenden Phase werden die unsichtbaren Pads in den inneren Schichten mit Röntgenstrahlen identifiziert. Die Röntgenanalyse ermöglicht die Erkennung der Pads und die Berechnung neuer Referenzbohrungen für das Bohren.

Bohren

Die Leiterplatte wird auf einer Hochgeschwindigkeits-CNC-Bohrmaschine (bis zu 280.000 Umdrehungen/Minute) hergestellt. Die gebohrten Löcher müssen so sauber und glatt wie möglich sein, um eine hochwertige Verkupferung der Löcher zu ermöglichen. Optional können bis zu 3 Platten übereinander gestapelt und gleichzeitig gebohrt werden.

Die Platten werden zwischen einer Grundplatte und einem oberen Aluminiumblech platziert. Die Grundplatte verhindert das Bohren in die Bohrmaschine und ermöglicht das Bohren tiefer als die Platte, wodurch Grate vermieden werden. Die Aluminium-Deckplatte vermeidet Grate und verhindert, dass der Bohrer abgelenkt wird. Beide Platten schützen die Oberflächen der Platte vor Beschädigungen und Kratzern.

Bürsten und Abschmieren

Nach dem Bohren wird die Oberfläche der Leiterplatte mechanisch mit einer oszillierenden und rotierenden Bürstenwalze gebürstet. Die gebohrten Löcher werden mit einer Permanganatlösung oder einem Sauerstoffplasma gereinigt, um Harz zu entfernen, das sich möglicherweise auf dem Kupfer abgesetzt hat. Harzrückstände auf dem Kupfer können die ordnungsgemäße elektrische Leitfähigkeit zwischen der Lochplattierung und den Leiterbahnen in den Schichten verhindern.

STROMLOSE BESCHICHTUNG

Stromlose Beschichtung

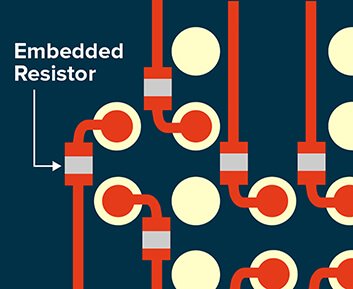

Um eine elektrische Verbindung zwischen den Bohrlöchern und allen Schichten herzustellen, wird mit chemischem Kupfer eine leitende Schicht von etwa 0,5-0,7 Mikron Dicke erzeugt. Diese leitfähige Schicht ist die Grundlage für das spätere Kupferplattenverfahren.

DECKSCHICHTEN UND BESCHICHTUNGEN

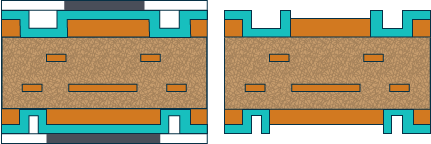

Dieses Verfahren ähnelt dem Verfahren zur Herstellung der inneren Schichten. Der Unterschied besteht darin, dass wir in diesem Schritt die Löcher sowie die Leiterbahnen und Pads der Außenschichten mit einem elektrolytischen Verkupferungsprozess beschichten.

Trockenfilmkaschierung von Außenschichten

Dieses Verfahren entspricht dem für die Innenschichten verwendeten Verfahren. Die Platte wird durch ein beheiztes Walzenpaar geführt (Temperatur: ca. 110º C Druck: 3-5 BAR). Die Cu-Oberfläche wird empfindlich für UV-Licht, daher erfolgt die weitere Bearbeitung nur im Gelblichtbereich.

Exposition und Entwicklung

Dieses Verfahren entspricht dem Verfahren in den inneren Schichten. Allerdings wird bei diesem Verfahren ein negativer Belichtungsprozess verwendet. Die Leiterdrähte sind nicht mit dem Resist bedeckt und können durch Verkupfern galvanisiert werden. Die Bereiche zwischen den Leiterbahnen werden mit polymerisiertem Laminat abgedeckt.

Elektrolytische Verkupferung

Alle Leiterbahnen und Löcher sind mit einer leitfähigen, galvanisch abgeschiedenen Kupferschicht überzogen. Die Löcher stellen die elektrische Verbindung zwischen den Leitern auf den Schichten her, und für eine gute Verbindung ist eine Kupferschicht von 20-25 Mikron an den Wänden des Lochs erforderlich. Die Gesamtkupferdicke auf den Außenschichten wird daher durch die Kupferdicke des Materials und die zusätzlichen 25-30 Mikrometer bestimmt, die beim Beschichtungsprozess hinzugefügt werden.

Verzinnung

Eine zweite Beschichtung dient dem Schutz der Kupferleiter während des anschließenden Ätzvorgangs, weshalb diese Schicht oft auch als Ätzresist bezeichnet wird.

Äußere Schicht Trockenabziehen der Folie

Die trockene Schicht wird entfernt, um die Kupferschicht für das Ätzen freizulegen.

ÄTZEN UND ENTFERNEN VON ZINN

Durch ein Ätzverfahren wird das überschüssige Kupfer entfernt, so dass nur noch die durch die Verzinnung geschützten Leiterbahnen und Pads kupferhaltig sind. Anschließend wird das Zinn mit Salpetersäure entfernt.

LÖTSTOPPMASKE

Die Lötstoppmaske wird auf die meisten Leiterplatten aufgebracht, um die Kupferoberfläche zu schützen, die während des Montageprozesses nicht durch das Löten geschützt wird, und um Lötkurzschlüsse während der Montage zu verhindern.

Die Platten werden gebürstet und gereinigt.

Die Platte ist auf beiden Seiten mit einer 15-25 Mikrometer starken Epoxid-Lötmaske beschichtet.

Mit Hilfe eines UV-Druckers und eines Fotofilms wird die Lötmaske an der Stelle gehärtet, an der die Lötmaske verbleiben soll.

Die Platten werden mit einem Entwickler bearbeitet, der die Lötstoppmaske von den zu belichtenden Bereichen trennt.

Das maskierte Lot wird in einem Ofen weiter gehärtet

OBERFLÄCHENBESCHICHTUNG

Mit der Oberflächenbehandlung wird eine lötbare Oberfläche auf die Kupferflächen aufgebracht, die nicht von der Lötmaske bedeckt sind. Diese Oberfläche schützt das Kupfer, bis die Bauteile zusammengesetzt und auf die Leiterplatten gelötet werden. Es sind verschiedene Oberflächenbehandlungen erhältlich. Die am häufigsten verwendeten sind HAL (Hot Air Leveling) und ENIG (Electroless Nickel Immersion Gold).

HAL

Beim HAL-Verfahren wird auf allen Pads ein Lot erzeugt. Die gesamte Platte wird in flüssiges Lot getaucht und mit heißer Druckluft aus dem Lot entfernt. Überschüssiges Lot (das sich nicht mit dem freiliegenden Kupfer verbunden hat) wird weggeblasen, und die Kupferpads und -löcher bleiben plattiert.

Das verwendete Lötmaterial ist entweder eine Zinn-Blei-Legierung oder nur Zinn (bleifrei).

ENIG

Dabei wird Nickel chemisch auf das Kupfer aufgebracht und anschließend eine dünne Goldschicht auf das Nickel. Der gesamte Prozess ist automatisiert, wobei die Platten durch eine Reihe von Tanks bewegt werden, das Kupfer gereinigt wird, eine 3-5 Mikrometer dicke Nickelschicht und eine Goldschicht von mindestens 0,05 Mikrometer aufgebracht wird.

Hartvergoldung

Kantenverbinder werden mit 1-1,5 Mikron Gold über 4-5 Mikron Nickel galvanisch beschichtet. Diese Art der Beschichtung ist für Fälle geeignet, in denen die Beschichtung der Erosion durch mehrfaches Einstecken standhalten muss.

LEGENDENDRUCK

Die Beschriftung wird mit einem Siebdrucker auf die Leiterplatte gedruckt.

ROUTING

Mit Hilfe einer CNC werden die Fertigungspaneele in einzelne Leiterplatten ausgeschnitten und die Leiterplatten entsprechend den Konstruktionsdaten in ihre Form gefräst.

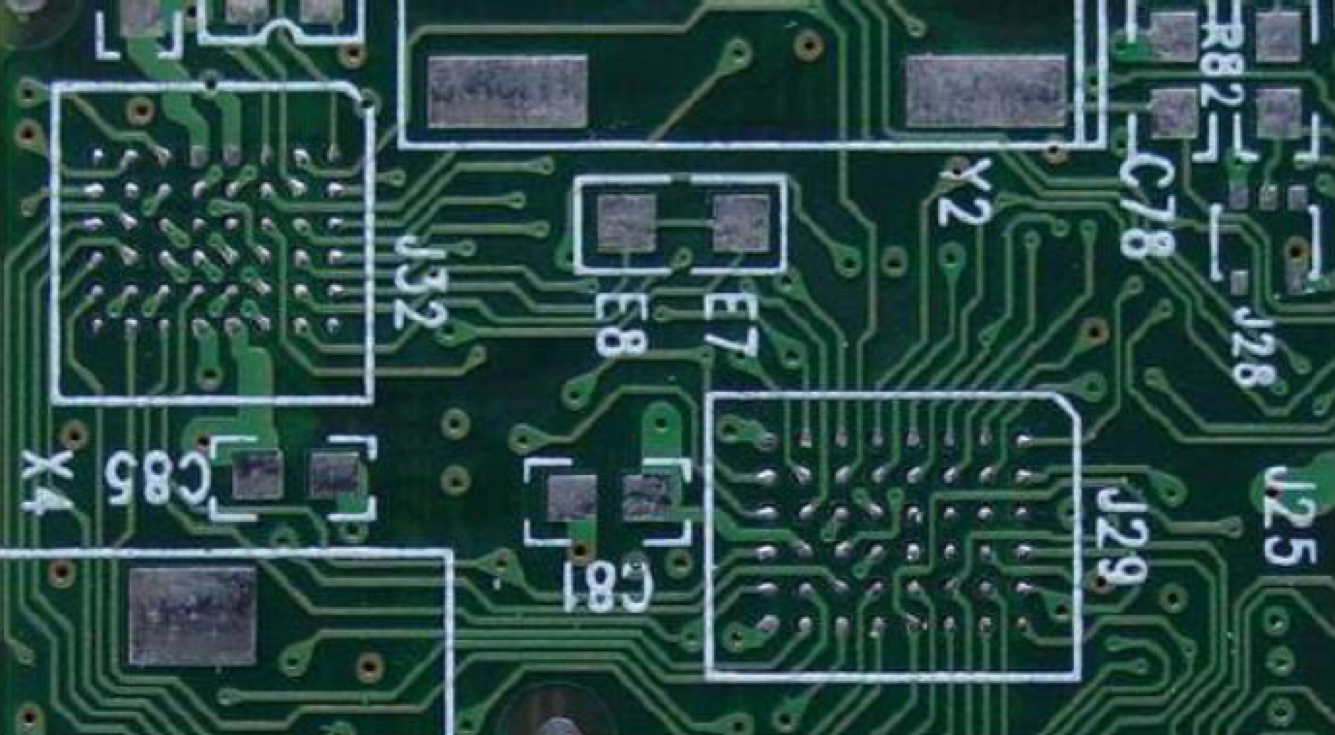

ELEKTRISCHE PRÜFUNG

Jede Leiterplatte wird anhand der Entwurfsdaten mit einem Nagelbettadapter oder einem Flying-Probe-Tester elektrisch getestet.

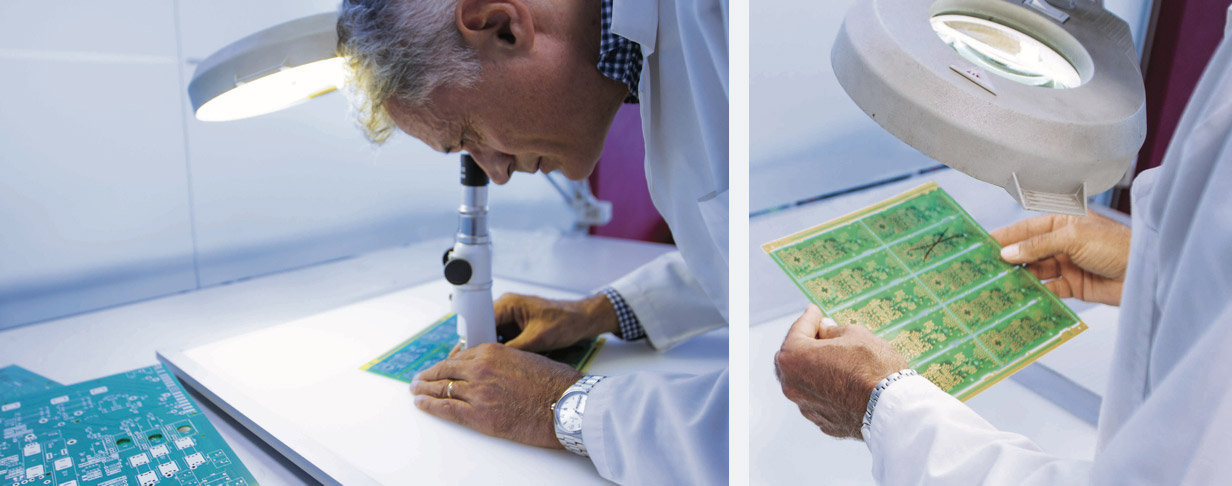

ABSCHLIESSENDE QUALITÄTSKONTROLLE

Dies ist die Endkontrolle des fertigen Leiterplattenprodukts. Sie prüft auf kosmetische Mängel wie Kratzer und Verunreinigungen, wobei IPC600 als Referenz dient.